**USB3FPGA**

User Manual C 1030-2805

## SPARTAN-3E FPGA board with USB 2.0 interface

Order number: C 1030-2805

# Copyright information

Copyright © 2007 CESYS GmbH. All Rights Reserved. The information in this document is proprietary to CESYS GmbH. No part of this document may be reproduced in any form or by any means or used to make derivative work (such as translation, transformation or adaptation) without written permission from CESYS GmbH.

CESYS GmbH provides this documentation without warranty, term or condition of any kind, either express or implied, including, but not limited to, express and implied warranties of merchantability, fitness for a particular purpose, and non-infringement. While the information contained herein is believed to be accurate, such information is preliminary, and no representations or warranties of accuracy or completeness are made. In no event will CESYS GmbH be liable for damages arising directly or indirectly from any use of or reliance upon the information contained in this document. CESYS GmbH will make improvements or changes in the product(s) and/or program(s) described in this documentation at any time.

CESYS GmbH retains the right to make changes to this product at any time, without notice. Products may have minor variations to this publication, known as errata. CESYS GmbH assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of CESYS GmbH products.

CESYS GmbH and the CESYS logo are registered trademarks.

All product names are trademarks, registered trademarks, or service marks of their respective owner.

$\Rightarrow$  Please check <u>www.cesys.com</u> to get the latest version of this document.

CESYS Gesellschaft für angewandte Mikroelektronik mbH Zeppelinstrasse 6a D – 91074 Herzogenaurach Germany

# A Overview

# Summary of USB3FPGA

USB3FPGA can be used as a development platform for designs with Xilinx SPARTAN 3E FPGAs as well as a OEM-component for job lot production. A 96-pin VG connector allows the attachment of external hardware to the FPGA. The board is equipped with a XC3S500E-4PQ208C XILINX FPGA, a member of the Spartan 3E family. This programmable logic device receives its internal functions after it has been configured by downloading a bitstream that represents the design. The change of logic functions (reconfiguration) is possible at any time.

The bistream is loaded from the PC via USB to the FPGA. The software that comes with the board permits to load new configurations anytime.

Two clock oscillators supply basic clocks that can be used by the FPGA. A third clock oszillator can be populated on request.

The 96-pin VG expansion connector of the USB3FPGA allows connections to I/O pins of the FPGA as well as to 3.3 V and GND. Many extensions can be attached directly without the need of an additional external power supply

# Feature list

- XILINX XC3S500E-4PQ208C FPGA

- CYPRESS FX2LP USB controller

- 2MByte FAST SRAM (1M x 16, 10ns) connected to FPGA

- 64 kByte SRAM connected to USB 2.0 controller (optional)

- USB 2.0 compliant device

- Selectable self-powered or bus-powered

- Up to three individual onboard clock oscillators

- Expansion port (44 IO pins + 15 INPUT pins + 22 auxiliary IO pins)

- 3 LEDS

- All FPGA Pins routed to test connectors

- Driver for Windows XP<sup>™</sup>, Firmware and Benchmark-program included

- Sample code (C++ Source) of test-program included

### Minimum requirements

- ☑ PC with USB 2.0 interface running Windows XP<sup>™</sup>

- ☑ 10 MByte free harddisk space

- ☑ USB3FPGA board with USB2.0 compliant cable

- ☑ CESYS USB 2.0 drivers

# FPGA Design Tools

To simulate and synthesize FPGA designs appropriate tools are needed. Xilinx offers a toolset called "ISE WebPack" free of charge on their website: <u>http://www.xilinx.com</u>. The ISE WebPack fully supports the XC3S500E Spartan3E-FPGA. There are also other commercial tools available from Xilinx and various other vendors.

# Windows XP Quick-start installation guide

- 1. Connect *USB3FPGA* to one free USB2.0 port with shipped USB2.0 compliant cable.

- 2. Install USB3FPGA driver via Windows XP<sup>™</sup> installation guide from included driver and utilities CD.

- 3. With Windows XP<sup>™</sup> USB3FPGA device driver has to be installed twice.

- 4. Locate folder "bin" on shipped CD and double-click "diag.exe". By pressing the 'Memory Test' button on the left a first device test can be started.

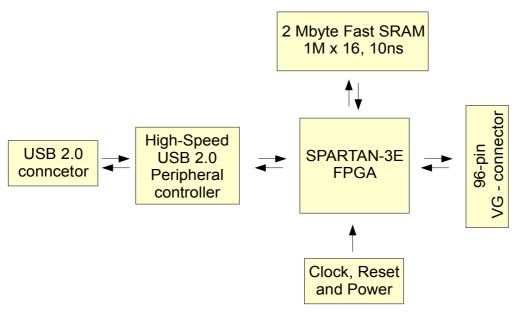

Figure 1: USB3FPGA block diagram

# SPARTAN-3E FPGA

| Device                | XC3S500E-4PQ208C |

|-----------------------|------------------|

| System Gates          | 500k             |

| CLB Rows              | 46               |

| CLB Columns           | 34               |

| Total CLBs            | 1164             |

| Total Slices          | 4.656            |

| Distributed RAM bits  | 73 k             |

| Block RAM bits        | 360 k            |

| Dedicated Multipliers | 20               |

| DCMs                  | 4                |

For details on SPARTAN-3E<sup>™</sup> FPGA, please refer to data sheet at: <u>http://www.xilinx.com/support/documentation/data\_sheets/ds312.pdf</u>

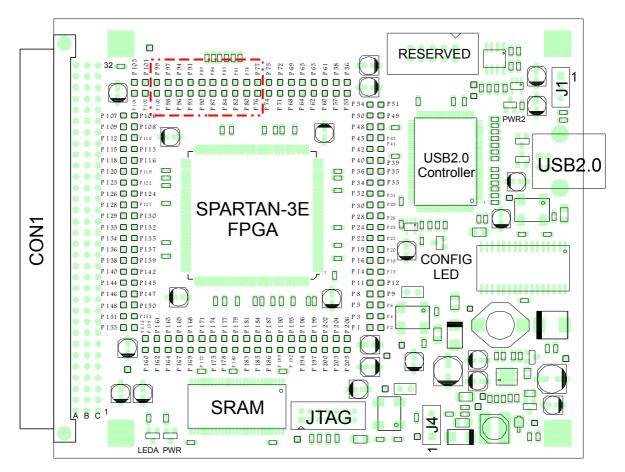

Connector diagram

Figure 2: USB3FPGA connector diagram

**<u>Attention</u>**: The Testpin numbering printed on the PCB v1.0 is not correct in the area marked above. This error has been fixed in PCB v1.1. This document is correct.

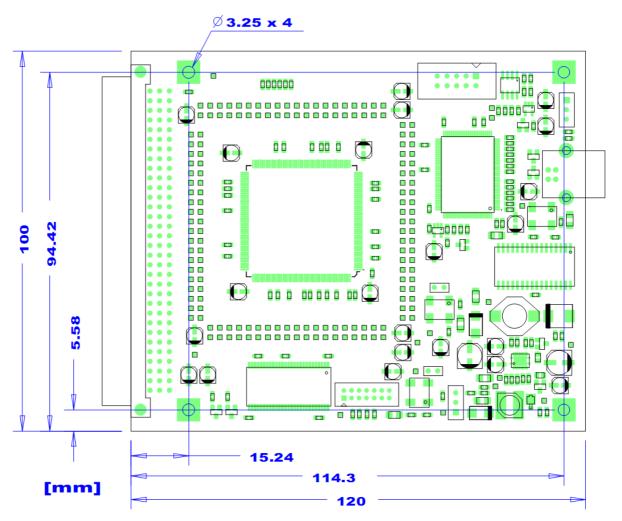

# Board dimensions

Figure 3: USB3FPGA board dimensions

### Power supply

The USB3FPGA can be configured to be self powered or bus powered. The default setting is "bus powered". This means power is provided by the USB bus. If the USB3FPGA is the only device on the USB bus, most computers should allow a maximum current of about 500 mA. This may not be true for notebooks.

| J1 Power source select |                                                                                 |

|------------------------|---------------------------------------------------------------------------------|

| Pin 1 – 2              | Self powered (External +5 Volt power supply must be attached to connector CON1) |

| Pin 2 – 3              | Bus powered (USB power supply)                                                  |

The option "self powered" requires an external power supply connected to CON1. Use this method if your design draws more current than your USB bus can deliver.

Attention: Be careful when using the external power connector. If you apply more than 5,5 Volts or if you reverse the polarity, the board will permanently fail and may not be reparable.

Directly after the USB3FPGA board is connected to the USB bus, it must not consume more then 100mA. This is the current limit (defined by the USB standard) until the software has called "SetConfiguration". Most PC's ignore this restriction but some USB-hubs measure the current-flow and will report a shortcut condition when a USB device draws more than 100 mA immediately after it has been plugged.

The option "software controlled" keeps the FPGA, the SRAM and the Pins on CON1 (A3, B3, C3) powered off until "SetConfiguration" was called. As long as the FPGA is not powered, its I/O pins must be held low (+/- 0.3 Volt).

Attention: When you use "software controlled" power-on behaviour, make sure no FPGA I/O pin is driven as long as the FPGA is not powered.

| J4 Optional power sequencing |                                                                                                                                                                                                    |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 1 – 2                    | All power supplies will ramp up as soon as +5 Volt are attached.                                                                                                                                   |

| Pin 2 – 3                    | Software controlled power on. At startup only FX2LP power supply will ramp up. Only after the attached USB host grants more than 100mA FX2LP will enable power up of other onboard power supplies. |

# USB 2.0 interface

The USB 2.0 interface of the board is implemented using an USB I/O controller outside the FPGA. Therefore FPGA designs do not need to include USB specific code. Developers do not need to know details about the USB bus. To enable communication between the FPGA and a program running on the PC, a easy-to-use API and VHDL sample code come with the board.

If your design works "stand-alone" and does not require any communication with the PC, you may ignore the USB interface details and use it only for downloading your design.

# FPGA pin connections

All FPGA VCCO-Pins on the USB3FPGA board are connected to 3,3 Volt. The I/O pins of the SPARTAN-3E FPGA do **NOT** accept 5 Volt Input signals.

When 5 Volt signals are connected without proper level-shifters or series resistors, the FPGA will immediately become damaged. When 3,3 Volt signals are used with long traces or cables in conjunction with improper termination, the resulting overshoot and undershoot can damage the FPGA as well. Please read Xilinx application note http://direct.xilinx.com/bvdocs/appnotes/xapp659.pdf for details.

Don't apply any voltage outside the interval [-0.5V....+3.8V], not even for a few Nanoseconds. Take care of overshoot / undershoot conditions.

# LEDs

| LEDs        |                              |

|-------------|------------------------------|

| USER- LED   | FPGA I/O pin 140             |

| Power- LED  | FPGA is powered ON           |

| Config- LED | FPGA is configured           |

| PWR2- LED   | USB controller is powered ON |

Power-LED lights up when the FPGA gets power.

PWR2-LED lights up when the board gets power from the USB-bus

Config-LED lights up when the FPGA is configured successfully.

User-LED light up when there is a low level at the corresponding FPGA Pin. The meaning of this LEDs is defined by the user's FPGA design.

# FPGA Testpins

All FPGA pins are routed to testpoints to ease the connection of measurement equipment like Logic Analyzers. The relationship between FPGA pins and Testpoints is printed on the USB3FPGA board and shown in the Connector-Diagram above.

# Expansion port CON1

The 96-pin "VG96 abc reverse" external expansion connector (DIN 41612) is of type "female". Please use the connector diagram to indicate pin 1. On some connectors, the numbers are printed upside down.

Mating connectors among others are: RS Components 476-025 or Farnell 104-986 or HARTING order number 0903 196 7921.

Most pins of the FPGA can be configured as input (IN), output (OUT), or bidirectional (I/O). Make sure your FPGA design does not drive pins that are already driven by external connected logic. This is also important for bi-directional signals.

| CON1 | 96-pin VG Expansion | connector          |                    |

|------|---------------------|--------------------|--------------------|

| Pin  | Α                   | В                  | С                  |

| 1    | V5EXT               | V5EXT              | V5EXT              |

| 2    | GND                 | GND                | GND                |

| 3    | V3                  | V3                 | V3                 |

| 4    | * FPGA I/O Pin 199  | * FPGA I/O Pin 197 | * FPGA I/O Pin 196 |

| 5    | ▼ FPGA IN Pin 194   | * FPGA I/O Pin 193 | * FPGA I/O Pin 192 |

| 6    | * FPGA I/O Pin 190  | * FPGA I/O Pin 189 | * FPGA I/O Pin 187 |

| 7    | ▼ FPGA IN Pin 175   | ▼ FPGA IN Pin 174  | * FPGA I/O Pin 172 |

| 8    | ▼ FPGA IN Pin 169   | * FPGA I/O Pin 168 | * FPGA I/O Pin 167 |

| 9    | * FPGA I/O Pin 161  | * FPGA I/O Pin 160 | ▼ FPGA IN Pin 159  |

| 10   | ▼ FPGA IN Pin 6     | ▼ FPGA IN Pin 204  | ▼ FPGA IN Pin 154  |

| 11   | * FPGA I/O Pin 153  | * FPGA I/O Pin 152 | * FPGA I/O Pin 151 |

| 12   | * FPGA I/O Pin 150  | ▼ FPGA IN Pin 148  | * FPGA I/O Pin 147 |

| 13   | * FPGA I/O Pin 146  | * FPGA I/O Pin 145 | * FPGA I/O Pin 144 |

| 14   | ▼ FPGA IN Pin 142   | * FPGA I/O Pin 9   | FPGA I/O Pin 139   |

| 15   | FPGA I/O Pin 138    | FPGA I/O Pin 137   | ▼ FPGA IN Pin 136  |

| 16   | FPGA I/O Pin 135    | FPGA I/O Pin 134   | FPGA I/O Pin 133   |

| 17   | FPGA I/O Pin 132    | ▼ FPGA IN Pin 130  | FPGA I/O Pin 129   |

| 18   | FPGA I/O Pin 128    | FPGA I/O Pin 127   | FPGA I/O Pin 126   |

| 19   | ▼ FPGA IN Pin 124   | FPGA I/O Pin 123   | FPGA I/O Pin 122   |

| 20   | FPGA I/O Pin 120    | FPGA I/O Pin 119   | ▼ FPGA IN Pin 118  |

| 21   | FPGA I/O Pin 116    | FPGA I/O Pin 115   | FPGA I/O Pin 113   |

| 22   | GND                 | GND                | GND                |

| 23   | FPGA I/O Pin 112    | ▼ FPGA IN Pin 110  | FPGA I/O Pin 109   |

| 24   | FPGA I/O Pin 108    | FPGA I/O Pin 107   | FPGA I/O Pin 106   |

| 25   | FPGA I/O Pin 55     | FPGA I/O Pin 61    | FPGA I/O Pin 62    |

| 26   | FPGA I/O Pin 63     | FPGA I/O Pin 64    | FPGA I/O Pin 65    |

| 27   | FPGA I/O Pin 68     | FPGA I/O Pin 69    | ▼ FPGA I/O Pin 71  |

| 28   | ▼ FPGA I/O Pin 72   | FPGA I/O Pin 90    | ▼ FPGA I/O Pin 91  |

| 29   | FPGA I/O Pin 93     | FPGA I/O Pin 94    | FPGA I/O Pin 96    |

| 30   | FPGA I/O Pin 97     | FPGA I/O Pin 98    | ▼ FPGA I/O Pin 101 |

| 31   | FPGA I/O Pin 99     | FPGA I/O Pin 100   | FPGA I/O Pin 102   |

| 32   | GND                 | GND                | GND                |

| V5EXT: | If Jumper J1 is set to Position 1-2 (self powered mode), a 5 VDC    |

|--------|---------------------------------------------------------------------|

|        | power-supply must be connected here. For bus-powered applications   |

|        | this pins can be left unconnected.                                  |

| V3:    | This pin is connected to the 3,3 Volt power supply of the board.    |

|        | Depending on the loaded FPGA design it can source up to 200 mA.     |

| *      | Attention:                                                          |

|        | This pin is also connected to the on-board RAM. It can only be used |

|        | when the RAM is not needed and disabled by pulling RAM_CE high.     |

| ▼      | Attention:                                                          |

This pin can only be used as an Input to the FPGA.

| Clock signals |                         |

|---------------|-------------------------|

| FX2CLK        | FPGA IN GCLK9 Pin 184   |

|               | FPGA I/O Pin 103        |

| IFCLK         | FPGA IN GCLK8 Pin 183   |

| CLK50         | FPGA I/O GCLK10 Pin 185 |

| CLK_optional  | FPGA I/O GCLK11 Pin 186 |

| RESET         | FPGA I/O Pin 28         |

### Clock signals and RESET

There are 4 clock sources on the USB3FPGA evaluation board. No matter which of them you use as the main clock for your design, you should synchronize all incoming asynchronous signals to it with at least one FlipFlop before using them internally. If you fail to do so, your design may work sometimes but not every time. One-hot state machines might lose their "hot"-state and become inoperable. Encoded state machines might enter wrong or illegal states.

#### FX2CLK

This is the clock, the USB controller FX2 uses internally and for its Program/Data memory interface.

#### IFCLK

This is the interface clock of the USB controller FX2 GPIF. If you want to transmit or receive data using the USB interface, it is the easiest way to choose this clock as the main clock source for your design. It defaults to 48 MHz. Its frequency can be switched to 30 MHz by the software (See API documentation).

#### CLK50

The CLK50 clock signal is connected to a on-board oscillator running at 50 MHz.

#### CLK\_optional

The CLK\_optional clock signal is connected to an empty oscillator position. Please contact CESYS if you need this clock.

#### RESET

The RESET-signal can be used as an active high input to reset the whole design. It is active during FPGA configuration and for a few milliseconds after configuration has finished. It also can get activated by the Host software.

# FPGA JTAG port

The JTAG port of the SPARTAN-3E FPGA is accessible through connector CON2. This 14-pin connector can be used with XILINX download cables. Although configuration of the FPGA can be made via USB, many other tools (i.e. ChipScope) require JTAG.

| CON2 JTAG connector |               |

|---------------------|---------------|

| Pin 1,3,5,7,9,11,13 | GND           |

| Pin 2               | +2,5 Volt     |

| Pin 4               | TMS           |

| Pin 6               | тск           |

| Pin 8               | TDO           |

| Pin 10              | TDI           |

| Pin 12,14           | Not connected |

Attention: Don't connect JTAG adapters that use 3,3 Volt signaling. The FPGA only accepts 2,5 Volt signal levels.

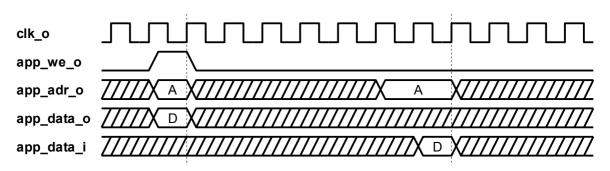

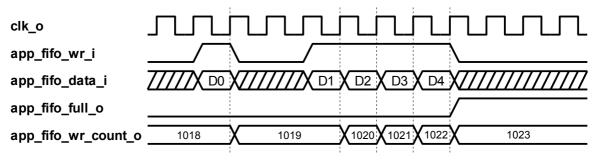

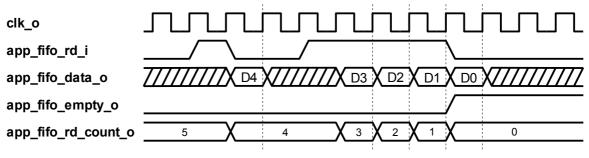

# Memory interface

CESYS USB3FPGA is equipped with 2MByte of FAST SRAM (1M x 16, 10ns, CYPRESS CY7C1061AV33-10ZC). This type of memory is static. This means it can be used very easily because it does not need refresh, bank management, address multiplexing or other techniques known from dynamic memories. The access time is 10ns. The maximum data rate is 200 MByte/s.

| FPGA <-> Memory interface |                  |

|---------------------------|------------------|

| SRAM signal name          | FPGA pin number  |

| RAM_A0                    | FPGA I/O Pin 189 |

| RAM_A1                    | FPGA I/O Pin 192 |

| RAM_A2                    | FPGA I/O Pin 196 |

| RAM_A3                    | FPGA I/O Pin 199 |

| FPGA <-> Memory interface |                  |  |

|---------------------------|------------------|--|

| SRAM signal name          | FPGA pin number  |  |

| RAM_A4                    | FPGA I/O Pin 202 |  |

| RAM_A5                    | FPGA I/O Pin 200 |  |

| RAM_A6                    | FPGA I/O Pin 197 |  |

| RAM_A7                    | FPGA I/O Pin 193 |  |

| RAM_A8                    | FPGA I/O Pin 190 |  |

| RAM_A9                    | FPGA I/O Pin 187 |  |

| RAM_A10                   | FPGA I/O Pin 171 |  |

| RAM_A11                   | FPGA I/O Pin 167 |  |

| RAM_A12                   | FPGA I/O Pin 164 |  |

| RAM_A13                   | FPGA I/O Pin 162 |  |

| RAM_A14                   | FPGA I/O Pin 160 |  |

| RAM_A15                   | FPGA I/O Pin 161 |  |

| RAM_A16                   | FPGA I/O Pin 163 |  |

| RAM_A17                   | FPGA I/O Pin 165 |  |

| RAM_A18                   | FPGA I/O Pin 168 |  |

| RAM_A19                   | FPGA I/O Pin 172 |  |

| RAM_D0                    | FPGA I/O Pin 150 |  |

| RAM_D1                    | FPGA I/O Pin 151 |  |

| RAM_D2                    | FPGA I/O Pin 152 |  |

| RAM_D3                    | FPGA I/O Pin 153 |  |

| RAM_D4                    | FPGA I/O Pin 144 |  |

| RAM_D5                    | FPGA I/O Pin 145 |  |

| RAM_D6                    | FPGA I/O Pin 146 |  |

| RAM_D7                    | FPGA I/O Pin 147 |  |

| RAM_D8                    | FPGA I/O Pin 203 |  |

| RAM_D9                    | FPGA I/O Pin 5   |  |

| RAM_D10                   | FPGA I/O Pin 8   |  |

| RAM_D11                   | FPGA I/O Pin 9   |  |

| RAM_D12                   | FPGA I/O Pin 2   |  |

| RAM_D13                   | FPGA I/O Pin 3   |  |

| RAM_D14                   | FPGA I/O Pin 4   |  |

| RAM_D15                   | FPGA I/O Pin 205 |  |

| RAM_WE#                   | FPGA I/O Pin 178 |  |

| FPGA <-> Memory interface |                  |

|---------------------------|------------------|

| SRAM signal name          | FPGA pin number  |

| RAM_OE#                   | FPGA I/O Pin 179 |

| RAM_CE#                   | FPGA I/O Pin 180 |

| RAM_BLE                   | FPGA I/O Pin 177 |

| RAM_BHE                   | FPGA I/O Pin 181 |

# **Undocumented IO**

FPGA IO pins that are not documented are reserved for USB communication and should not be connected in user designs.

# C Software

# Files

The files which ships with our source package are sorted in subdirectories, the structure is described below.

| Folder  | Contains                                                                                                                                                                                                             |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bin     | Compiled sample applications, including the diagnostic tool<br>'diag.exe' which is can be used for simple tasks like device testing<br>and FPGA configuration. How to use it can be found later in this<br>document. |

| designs | Holds the generated design which is used for all of our sample applications, including the diagnostic tool. Source code can be found in the source folder.                                                           |

| doc     | All documentation, including this document can be found here.                                                                                                                                                        |

| drivers | System drivers for our device is located in this folder, if the operating system asks for a driver, point it to this folder.                                                                                         |

| source  | Source files, for the FPGA and the host system, mainly sample applications can be found in this folder, in addition, the API is located in subfolders 'lib' and 'include'.                                           |

### Driver installation

After plugging the device to a PC the first time, the operating system, in this case Windows XP will pop up an information about the detection of a new hardware. As Windows doesn't know the USB3FPGA board, it asks the user several questions to install the correct drivers for the device. The steps are shortly described below:

In the first Dialog, select the second option, 'Install from a list or specific location (Advanced)', press 'Next'. In the second dialog, select the first option 'Search for the best driver in these location.' and include only the second option there, 'Include this location in the search:'. Then press 'Browse' and select the 'drivers' folder which is included in the source package that ships with our board, press 'Next'. Windows will try to install the driver now, for security reasons it will ask the user to allow this via another dialog box, you have to select 'Continue Anyway' here. Finish the installation by pressing 'Finish' in the next dialog box, the loader driver is installed now. Because the used USB chip needs a two step driver loading mechanism, Windows will now pop up another dialog which informs the user about a new hardware detection. To install this second driver, follow the installation instructions for first driver step by step, this will be exactly the same. After finishing the installation for the second driver, the device should work correctly. To verify the installation, have a look in the device manager, expand the 'Universal Serial Bus controllers' tree and look for a device named 'Cesys USB3FPGA compatible device'. In addition, start the diagnostic tool which is located in the 'bin' folder in our source

package and try the memory test and benchmark options there. How this works is described in the following chapter.

# Diagnostics

| Ceusb3 Diagnostics |                                                                                | × |

|--------------------|--------------------------------------------------------------------------------|---|

| <b>CES\S</b>       | \\?\usb#vid_10f8&pid_c381#5&f635d31&0&5#{53b029df-bbc6-4db8-841e-69ce4f163588} |   |

| ReEnum Device List |                                                                                |   |

| Device Info        |                                                                                |   |

| Download Design    |                                                                                |   |

| Dump EEPROM        |                                                                                |   |

| RBT to BIN         |                                                                                |   |

| Register I/O       |                                                                                |   |

| Memory Test        |                                                                                |   |

|                    |                                                                                |   |

| Benchmark          |                                                                                |   |

| Close              |                                                                                |   |

Figure 4: Ceusb3 Diagnostics

The list box on top of the window lists all available devices. All device specific operations are bound to the device selected in this box. After a change in the hardware configuration (device plug, unplug, replug), this list has to be re-enumerated to ensure stability and functionality. This can be done by simply pressing the '**ReEnum Device List**' button.

To get detailed information about a selected device, a click on '**Device Info**' will print all known information to the log window below the device list box. This includes information about the driver, firmware, hardware composition plus some software details.

The devices main functionality is given by the on board FPGA, which must be configured to work (which is not case after power on). The configuration process is quite simply, after clicking the 'Download Design' button, a file selection dialog will pop up, the chosen file will be used to configure the FPGA after the selection. Two file types are supported at the moment, .RBT (raw bit streams) and .FPGA (binary equivalents for raw bit streams, creation described below).

The 'Dump EEPROM' button will pop up a file selection dialog, where users can choose a file where all EEPROM contents will be stored in a hexadecimal like text format.

As described above the design importer is able to use .RBT and .FPGA files. The .FPGA format is simply a binary representation for .RBT files, which are smaller than there .RBT equivalents and they will be parsed much faster. To create a .FPGA out of a .RBT, a click on '**RBT to BIN**' will pop up a source selection dialog. Afterwards a

destination file must be chosen in a second file selection dialog, thats all, the conversion should be done.

The 'Register I/O' button hides the log window and pops up additional controls to test the register read and write functionality based on the underlying FPGA design, a compatible design must be downloaded. The 'Write' button writes the given value to the selected register, just as the 'Read' button reads the value from the selected register and displays the value in the 'Value' field. The 'Return' button on the left return to normal functionality.

| Ceusb3 Diagnostics |                                                                                | × |

|--------------------|--------------------------------------------------------------------------------|---|

| <b>CESYS</b>       | \\?\usb#vid_10f8&pid_c381#5&f635d31&0&5#{53b029df-bbc6-4db8-841e-69ce4f163588} |   |

| ReEnum Device List | Register: 0x0000 Value: 0x0000                                                 |   |

| Device Info        | Write Read                                                                     |   |

| Download Design    |                                                                                |   |

| Dump EEPROM        |                                                                                |   |

| RBT to BIN         |                                                                                |   |

| Return             |                                                                                |   |

| Memory Test        |                                                                                |   |

|                    |                                                                                |   |

| Benchmark          |                                                                                |   |

| Close              |                                                                                |   |

Figure 5: Ceusb3 Diagnostics: Register I/O

The 2 MB on board memory can be tested by pressing the 'Memory Test' button. A message box will pop up afterwards, showing the results of the test, either success or failure.

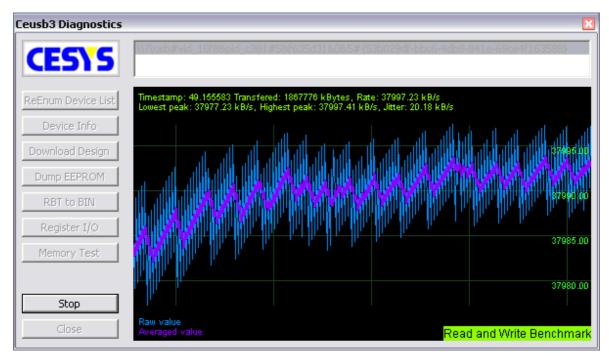

The 'Benchmark' button shows a list of 3 different benchmark options, Read, Write, Read and Write. After choosing one of these options, the log window disappears and the benchmark graph pops up. The blue graph line shows the unchanged value of bytes per second transferred between PC and device, while the purple line shows an averaged value. Benchmarking can be stopped by pressing the 'Stop' button on the left.

Figure 6: Ceusb3 Diagnostics: Benchmark

# API

### General

#### Language compatibility

The CEUSB3 API is designed to work with C++ native code to ensure best performance. Due to the wide popularity the library is compatible with Visual C++ 7.1 and higher versions. In addition to this, a wrapper for the .NET Framework 1.1 is also available, so applications written in C++ NET, C# and Visual Basic have access to the API too. The NET wrapper consists of the same classes and methods as the C++ API, but global functions, macros and constants are encapsulated in an additional class (ceUSB3API), based on the fact that NET doesn't support this. Furthermore some data types are not available in all languages, so a few of the parameters have a different value type in the C++ and .NET API. The best place to analyze the differences are the sample sources that ship with the API. The test application shows many parts from the API and is available in C++ native (cntest), C++ NET (cnettest), C# (cstest) and VB (vbtest).

### Backward compatibility

The CEUSB3 API is newly designed so there's no compatibility with API's from USB2FPGA or other devices.

#### ceUSB3 C++ API specs

#### Basics

The API contains the necessary library and include files. To use the API you have to follow the steps below:

- Include the main header file (ceusb3api.h).

- Link the executable with the main library (ceusb3api.lib).

The whole API is located in namespace ceUSB3, so either tell the compiler to use this namespace (using namespace ceUSB3;) or scope all elements with this namespace separately (e.g. ceUSB3::ceDevice \*pDev = ceUSB3::ceDevice::GetDevice(0);). Pointers retrieved by the API must NOT be deleted, this is done by the API internally. Affected classes are ceDevice and ceInfo.

#### Error handling

Most functions return a HRESULT code, so you can use the SUCCEEDED() and FAILED() macros defined in the windows API. To retrieve a printable error string from a failed call use GetHRESULTMessage(), which returns the description string of a given error code (Only error codes used by the API).

#### ceUSB3 NET API specs

#### Basics

The API can be used by adding a new reference to the project, choose the file browser there and select ceusb3apinet.dll. To be able to use the classes, namespace cesys.ceUSB3NET must be used, the syntax is based on the NET language that is used.

#### Error handling

Most functions return a System::Int32 code, the C++ macros for error checking are encapsulated in two static methods, ceUSB3API.ceSUCCEEDED() and ceUSB3API.ceFAILED(). In addition, all possible error codes used by the API are defined as constants in that class (ceUSBAPI.ceS\_\* / ceUSBAPI.ceE\_\*). To retrieve a printable error string from a failed call use ceUSB3API.GetHRESULTMessage(), which returns the description string of a given error code (Only error codes used by the API).

#### Additional differences to the C++ API

Because NET doesn't support global functions, Init() and Delnit() are encapsulated in class ceUSB3API too. Furthermore Init() doens't expect a GUID, but a value from the ceUSB3API.ceDeviceType enumeration.

#### How to use the API

#### Initialization / Deinitialization

To use the API it must be initialized, this is done by a call to Init() (NET: ceUSB3API.Init()). This function searches for all devices plugged to the computer which matches the given GUID (NET: ceUSB3API.ceDeviceType). You can call this function with different GUID's which builds an internal list of all of them.

After using the API it must be freed, this is done by calling **Delnit()** (NET:

ceUSB3API::Delnit()). To detect any changes in the list of connected devices, you have to call Delnit() and start again with one or more lnit() - calls. This forces a reenumeration of all devices. Attention! This invalidates all pointers you get from the API!

#### How to communicate with devices

If the API is initialized correctly, you can retrieve the count of available devices by calling the static member function GetDeviceCount() from class ceDevice. To access one of the devices, call function GetDevice() from the same class and use an index in range of 0 < index < GetDeviceCount() to specify one of the devices. The pointer returned by this function is constant and valid until you call Delnit() (the same call will return the same pointer, so you do not have to store this pointer anywhere).

All communication with the device is done using this class pointer. Before any data can be sent or received, the device must be opened. To do this call method Open() which internally opens the device, set default parameters and retrieves some information about the device. After a successful call to this function you can do those things (descriptions below):

- Configure device (SetGPIFSpeed()).

- Retrieve information (GetInfo()).

- Download FPGA designs (ProgramFPGA()).

- Read and write FPGA registers (ReadRegister()/WriteRegister()).

- Read and write huge blocks of data (ReadBulk()/WriteBulk()).

- Read and write parts of the EEPROM (ReadEeprom()/WriteEeprom()).

To properly finish the use of the device, call Close().

#### Function description (methods in alphabetic order)

All methods are listed twice, the first one is the C++ native notation, the other one is the NET counterpart in C# notation.

# Global functions (NET: class ceUSB3API)

| C++:    | <pre>void DeInit()</pre>                                                                      |

|---------|-----------------------------------------------------------------------------------------------|

| NET:    | <pre>void ceUSB3API.DeInit()</pre>                                                            |

| Info    | Frees all resources allocated by $\texttt{Init}()$ , this must be called after using the API. |

| Returns | -                                                                                             |

| Errors  | -                                                                                             |

| C++:    | const char *GetHRESULTMessage(HRESULT hr)                  |

|---------|------------------------------------------------------------|

| NET:    | String ceUSB3API.GetHRESULTMessage(System.Int32 hr)        |

| Info    | Returns the error string bound to the given error code hr. |

| Returns | Error string                                               |

| Errors  | -                                                          |

| C++:    | HRESULT Init(const GUID &Guid)                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NET:    | <pre>Int32 ceUSBAPI.Init(ceUSB3API.DeviceType T)</pre>                                                                                                                                                                                                                                                                                                                                                            |

| Info    | Initializes the API and searches for devices with the given type (via<br>GUID or device type). The function can be called multiple times with<br>different types to enumerate and use different devices. Resources<br>allocated by that call must be freed by calling DeInit() after use.<br>Possible GUID's (C++):<br>GUID_INTERFACE_CEUSB3<br>GUID_INTERFACE_PSAA4096V2<br>Possible Types (NET):<br>ceDT_CEUSB3 |

|         | ceDT_PSAA4096V2                                                                                                                                                                                                                                                                                                                                                                                                   |

| Returns | Error code                                                                                                                                                                                                                                                                                                                                                                                                        |

| Errors  | S_OK: no error                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | E_FAIL: error searching devices                                                                                                                                                                                                                                                                                                                                                                                   |

### class ceDevice

| C++:    | HRESULT ceDevice::Abo                         | rtPipe(uint uiPipeNumber)                                                       |

|---------|-----------------------------------------------|---------------------------------------------------------------------------------|

| NET:    | Int32 ceDevice.AbortPipe(UInt32 uiPipeNumber) |                                                                                 |

| Info    | Forces the USB bus driver to (uiPipeNumber).  | abort the transfer on a given pipe                                              |

| Returns | Error code                                    |                                                                                 |

| Errors  | E_OPEN: d<br>E_FAIL: c                        | o error<br>evice not open<br>all to driver fails<br>iPipeNumber is out of range |

| C++:    | <pre>void ceDevice::Close()</pre> |

|---------|-----------------------------------|

| NET:    | <pre>void ceDevice.Close()</pre>  |

| Info    | Closes the device.                |

| Returns | -                                 |

| Errors  | -                                 |

| C++:    | <pre>HRESULT ceDevice::GetAsyncResult(ceAsyncHandle *pH, uint *uiTransfered)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NET:    | <pre>Int32 ceDevice::GetAsyncResult(ref ceAsyncHandle pH, ref UInt32 uiTransfered)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | This method is needed when using any of the following functions<br>using the async call convention: ReadBulk(), WriteBulk().<br>Usage: After starting an async operation, use the async handle (pH)<br>to check if the transfer is complete. Afterwards you have to call<br>GetAsyncResult() to cleanup the call and retrieve the count of<br>bytes transferred via this operation (uiTransfered).<br>A good example on how to use this can be found in the test<br>application that ships with the API, which is available in all supported<br>languages. |

| Returns | Error code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Errors  | S_OK:no errorE_FAIL:the function failsE_INVALIDARG:pH is NULL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| C++:    | <pre>ceDevice *ceDevice::GetDevice(uint uiIdx)</pre>                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NET:    | ceDevice ceDevice.GetDevice(UInt32 uiIdx)                                                                                                                                                   |

| Info    | Returns a pointer to a device which is selected by a zero based index (uildx). This pointer is valid until DeInit() is called. Never try to delete this object, this is done automatically. |

| Returns | Pointer to device with the given index, NULL otherwise.                                                                                                                                     |

| Errors  | -                                                                                                                                                                                           |

| C++:    | <pre>uint ceDevice::GetDeviceCount()</pre>                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------|

| NET:    | UInt32 ceDevice.GetDeviceCount()                                                                                               |

| Info    | Returns the count of devices find during the call of Init(), if Init() is called multiple times, the total number is returned. |

| Returns | Count of devices found in the system.                                                                                          |

| Errors  | -                                                                                                                              |

| C++:    | <pre>ceInfo *ceDevice::GetInfo()</pre>                                                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NET:    | ceInfo ceDevice.GetInfo()                                                                                                                                                                                     |

| Info    | Returns a static pointer to a ceInfo class instance bound to the device. This holds additional information about the device. Never try to delete the returned object, this is done by DeInit() automatically. |

| Returns | Pointer to info class.                                                                                                                                                                                        |

| Errors  | _                                                                                                                                                                                                             |

| C++:    | <pre>uint ceDevice::GetLastError()</pre>                                                    |

|---------|---------------------------------------------------------------------------------------------|

| NET:    | UInt32 ceDevice.GetLastError()                                                              |

| Info    | Returns the last error occurred in the driver. This may help to find out unexpected errors. |

| Returns | Driver error code.                                                                          |

| Errors  | -                                                                                           |

| C++:    | <pre>uint ceDevice::GetLastFirmwareError()</pre>                                              |

|---------|-----------------------------------------------------------------------------------------------|

| NET:    | <pre>UInt32 ceDevice.GetLastFirmwareError()</pre>                                             |

| Info    | Returns the last error occurred in the firmware. This may help to find out unexpected errors. |

| Returns | Firmware error code.                                                                          |

| Errors  | -                                                                                             |

| C++:    | HRESULT ceDevice::Open()                                                                                    |  |

|---------|-------------------------------------------------------------------------------------------------------------|--|

| NET:    | Int32 ceDevice.Open()                                                                                       |  |

| Info    | Opens the device.                                                                                           |  |

| Returns | Error code.                                                                                                 |  |

| Errors  | S_OK:no errorS_FALSE:device already openE_FAIL:error retrieving informationfrom driverfailed to open device |  |

| C++:    | HRESULT ceDevice::ProgramFPGA(ceFPGA *pFPGA)<br>Int32 ceDevice.ProgramFPGA(ceFPGA pFPGA)                                                                |                                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Info    | Downloads a FPGA design to the device. This should be the first step after opening the device. Without a running design the hardware won't do anything. |                                                                                                                                                        |

| Returns | Error code.                                                                                                                                             |                                                                                                                                                        |

| Errors  | S_OK:<br>E_OPEN:<br>E_FAIL:<br>E_INVALIDARG:<br>E_NOPIPE:<br>E_FPGA_INIT:<br>E_FPGA_NC:                                                                 | no error<br>device not open<br>call to driver fails<br>invalid design<br>no matching pipe found<br>fpga init pin doesn't switch<br>fpga not configured |

| C++:<br>NET: | <pre>HRESULT ceDevice::ReadBulk(uchar *pucData, uint<br/>uiSize, uint &amp;uiTransfered, ceAsyncHandle *pH,<br/>uint uiPipe, uint uiTimeOut)<br/>Int32 ceDevice.ReadBulk(Byte[] pucData, UInt32<br/>uiSize, ref UInt32 uiTransfered, ref ceAsyncHandle<br/>pH, UInt32 uiPipe, UInt32 uiTimeOut)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Info         | pH, UInt32 uiPipe, UInt32 uiTimeOut) This function should be used to transfer huge blocks of data from device to host. It is able to work in sync or async mode, depending on the given parameters. Parameter pucData should point to a buffer that is able to hold the requested data, while uiSize must be data count of bytes that should be received. The maximum allowed count of bytes in one call can be retrieved by method GetPipeBufferSize() from attached class celnfo (use GetInfo() to get it). Furthermore this count must be dividable by 512. If pH is NULL, than synced I/O is active, if pH is a valid async handle, async I/O will be used. Using synced I/O, uiTransfered will return the count of bytes transferred, which can be unequal to the requested transfer count, otherwise this return value is undefined. To specify a special pipe for the transfer, uiPipe can be used, but in most cases a value of 0xfffffff let the API decide the best pipe. The last parameter, uiTimeOut is only valid using synced I/O, a timeout for transfer completion in milliseconds can be specified here. |  |

| Returns      | Error code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Errors       | S_OK: no error<br>E_OPEN: device not open<br>E_FAIL: call to driver fails<br>E_INVALIDARG: invalid data ptr, uiSize = 0<br>or uiSize not dividable by 512<br>E_NOPIPE: no matching pipe found/uiPipe<br>invalid<br>E_TIMEOUT: call is timed out (sync)<br>E_PENDING: device is in pending mode<br>(async)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| C++:    | <pre>HRESULT ceDevice::ReadEeprom(uint uiAddress, uchar *pucData, uint uiSize)</pre>                                                                                                                                                                                              |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NET:    | <pre>Int32 ceDevice.ReadEeprom(uint uiAddress, Byte[] pucData, UInt32 uiSize)</pre>                                                                                                                                                                                               |

| Info    | Reads data from on board EEPROM. 7 KB are free for use, starting<br>at address 0. Maximum transfer size is 4 KB. uiAddress sets the<br>base offset, pucData should be huge enough to hold the requested<br>data, while uiSize sets the count of bytes that should be transferred. |

| Returns | Error code.                                                                                                                                                                                                                                                                       |

| Errors | S_OK:no errorE_OPEN:device not openE_FAIL:call to driver fails    |

|--------|-------------------------------------------------------------------|

|        | E_INVALIDARG: uiAddress+uiSize > 7k, uiSize>4096 or<br>0==pucData |

| C++:    | <pre>HRESULT ceDevice::ReadRegister(ushort usAddress,<br/>ushort &amp;usValue)</pre> |  |

|---------|--------------------------------------------------------------------------------------|--|

| NET:    | <pre>Int32 ceDevice.ReadRegister(UInt16 usAddress, ref UInt16 usValue)</pre>         |  |

| Info    | Read the value of FPGA register usAddress, the result will be stored in usValue      |  |

| Returns | Error code.                                                                          |  |

| Errors  | S_OK:no errorE_OPEN:device not openE_FAIL:call to driver fails                       |  |

| C++:    | HRESULT ceDevice::ResetFPGA()                                  |  |

|---------|----------------------------------------------------------------|--|

| NET:    | Int32 ceDevice.ResetFPGA()                                     |  |

| Info    | Pulses the FPGA reset pin.                                     |  |

| Returns | Error code.                                                    |  |

| Errors  | S_OK:no errorE_OPEN:device not openE_FAIL:call to driver fails |  |

| C++:    | HRESULT ceDevice::ResetPipe(uint uiPipeNumber)               |                                                                            |

|---------|--------------------------------------------------------------|----------------------------------------------------------------------------|

| NET:    | Int32 ceDevice.ResetPipe(UInt32 uiPipeNumber)                |                                                                            |

| Info    | Forces the USB bus driver to reset pipe number uiPipeNumber. |                                                                            |

| Returns | Error code.                                                  |                                                                            |

| Errors  | E_OPEN: de<br>E_FAIL: ca                                     | error<br>evice not open<br>all to driver fails<br>.PipeNumber out of range |

| C++: | HRESULT ceDevice:SetGPIFSpeed(ceGPIFSpeed Speed) |

|------|--------------------------------------------------|

| NET: | Int32 ceDevice.SetGPIFSpeed(ceDevice.ceGPIFSpeed |

|         | Speed)                                                                                                                                                                                                                               |                                                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Info    | Allows the adjustment of the GPIF speed between 30 and 48 MHz.<br>Default value is 48 MHz. It is not necessary to change this value<br>except for some special cases.<br>Possible enumerators are:<br>ceGPIFS_30MHz<br>ceGPIFS_48MHz |                                                                                  |

| Returns | Error code.                                                                                                                                                                                                                          |                                                                                  |

| Errors  | S_OK:<br>E_OPEN:<br>E_FAIL:<br>E_INVALIDARG:                                                                                                                                                                                         | no error<br>device not open<br>call to driver fails<br>uiPipeNumber out of range |

| C++:<br>NET: | <pre>HRESULT ceDevice::WriteBulk(uchar *pucData, uint<br/>uiSize, uint &amp;uiTransfered, ceAsyncHandle *pH,<br/>uint uiPipe, uint uiTimeOut)<br/>Int32 ceDevice.WriteBulk(Byte[] pucData, UInt32<br/>uiSize, ref UInt32 uiTransfered, ref ceAsyncHandle<br/>pH, UInt32 uiPipe, UInt32 uiTimeOut)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Info         | pH, UInt32 uiPipe, UInt32 uiTimeOut) This function should be used to transfer huge blocks of data from host to device. It is able to work in sync or async mode, depending on the given parameters. Parameter pucData should point to the buffer which contains the data to send, while uiSize must be data count of bytes that should be transfered. The maximum allowed count of bytes in one call can be retrieved by method GetPipeBufferSize() from attached class celnfo (use GetInfo() to get it). Furthermore this count must be even. If pH is NULL, than synced I/O is active, if pH is a valid async handle, async I/O will be used. Using synced I/O, uiTransfered will return the count of bytes transferred, which can be unequal to the requested transfer count, otherwise this return value is undefined. To specify a special pipe for the transfer, uiPipe can be used, but in most cases a value of 0xfffffff let the API decide the best pipe. The last parameter, uiTimeOut is only valid using synced I/O, a timeout for transfer completion in milliseconds can be specified here. |  |

| Returns      | Error code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Errors       | S_OK: no error<br>E_OPEN: device not open<br>E_FAIL: call to driver fails<br>E_INVALIDARG: invalid data ptr, uiSize = 0<br>or uiSize not dividable by 512<br>E_NOPIPE: no matching pipe found/uiPipe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| invalid    |                           |

|------------|---------------------------|

| E_TIMEOUT: | call is timed out (sync)  |

| E_PENDING: | device is in pending mode |

| (async)    |                           |

| C++:    | <pre>HRESULT ceDevice::WriteEeprom(uint uiAddress,<br/>uchar *pucData, uint uiSize)<br/>Int32 ceDevice.WriteEeprom(uint uiAddress, Byte[]</pre>                                                                                           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INE I.  | pucData, UInt32 uiSize)                                                                                                                                                                                                                   |

| Info    | Writes data to on board EEPROM. 7 KB are free for use, starting at address 0. Maximum transfer size is 4 KB. uiAddress sets the base offset, pucData must hold the data, while uiSize sets the count of bytes that should be transferred. |

| Returns | Error code.                                                                                                                                                                                                                               |

| Errors  | S_OK: no error<br>E_OPEN: device not open<br>E_FAIL: call to driver fails<br>E_INVALIDARG: uiAddress+uiSize > 7k,<br>uiSize>4096 or 0==pucData                                                                                            |

| C++:    | HRESULT ceDevice::WriteRegister(ushort usAddress,<br>ushort &usValue) |

|---------|-----------------------------------------------------------------------|

| NET:    | Int32 ceDevice.WriteRegister(UInt16 usAddress, ref<br>UInt16 usValue) |

| Info    | Write value usValue to FPGA register usAddress                        |

| Returns | Error code.                                                           |

| Errors  | S_OK:no errorE_OPEN:device not openE_FAIL:call to driver fails        |

### class celnfo

| C++:    | <pre>const char *ceInfo::GetDeviceName()</pre>                              |

|---------|-----------------------------------------------------------------------------|

| NET:    | String ceInfo.GetDeviceName()                                               |

| Info    | Returns the name of the device (Same name as listed in the device manager). |

| Returns | Requested information.                                                      |

| Errors  | -                                                                           |

| C++:    | <pre>const char *ceInfo::GetDevicePath()</pre>                                            |

|---------|-------------------------------------------------------------------------------------------|

| NET:    | <pre>String ceInfo.GetDevicePath()</pre>                                                  |

| Info    | Returns the internal name of windows path to the device. For informational purposes only. |

| Returns | Requested information.                                                                    |

| Errors  | -                                                                                         |

| C++:    | <pre>const char *ceInfo::GetDriverInfo()</pre>                                           |

|---------|------------------------------------------------------------------------------------------|

| NET:    | String ceInfo.GetDriverInfo()                                                            |

| Info    | Returns the description and version of the used driver. For informational purposes only. |

| Returns | Requested information.                                                                   |

| Errors  | -                                                                                        |

| C++:    | <pre>const char *ceInfo::GetFirmwareInfo()</pre>                                           |

|---------|--------------------------------------------------------------------------------------------|

| NET:    | <pre>String ceInfo.GetFirmwareInfo()</pre>                                                 |

| Info    | Returns the description and version of the used firmware. For informational purposes only. |

| Returns | Requested information.                                                                     |

| Errors  | -                                                                                          |

| C++:    | <pre>const char *ceInfo::GetHostController()</pre>                                                           |

|---------|--------------------------------------------------------------------------------------------------------------|

| NET:    | String ceInfo.GetHostController()                                                                            |

| Info    | Returns the description of the host controller this device is connected to. For informational purposes only. |

| Returns | Requested information.                                                                                       |

| Errors  | -                                                                                                            |

| C++:    | <pre>uint ceInfo::GetPipeBufferSize()</pre>                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| NET:    | <pre>UInt32 ceInfo.GetPipeBufferSize()</pre>                                                                                                   |

| Info    | Returns the buffer size of each pipe inside the driver. This is the maximum count of bytes usable by block transfers via <pre>ReadBulk()</pre> |

| Returns | Requested information.                                                                                                                         |

| Errors  | -                                                                                                                                              |

| C++:    | <pre>uint ceInfo::GetPipeCount()</pre>                                                          |

|---------|-------------------------------------------------------------------------------------------------|

| NET:    | <pre>UInt32 ceInfo.GetPipeCount()</pre>                                                         |

| Info    | Count of pipes supported by the current host-device interface. For informational purposes only. |

| Returns | Requested information.                                                                          |

| Errors  | -                                                                                               |

| C++:    | <pre>const char *ceInfo::GetUSBPath()</pre>                                                                                                                     |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NET:    | <pre>String ceInfo.GetUSBPath()</pre>                                                                                                                           |

| Info    | Returns the connection path from device to host controller, including<br>any hub in between. Used ports are enclosed in squared brackets in<br>back of any hub. |

| Returns | Requested information.                                                                                                                                          |

| Errors  | _                                                                                                                                                               |

| C++:    | <pre>bool ceInfo::GetUSBPath()</pre>                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------|

| NET:    | Boolean ceInfo.GetUSBPath()                                                                                        |

| Info    | Returns true if the transfer between host and device is in highspeed mode (480MBit/s), false otherwise (15MBit/s). |

| Returns | Requested information.                                                                                             |

| Errors  | -                                                                                                                  |

#### class ceFPGA

This class is able to import and export different formats of FPGA designs. This time, rawbit (.RBT) and binary streams (.FPGA, cesys internally used format) are supported. Except ceDevice and ceInfo this class has an public constructor and destructor, so you have to take care about the lifetime of this object.

| C++:    | ceFPGA::ceFPGA()   |

|---------|--------------------|

| NET:    | ceFPGA.ceFPGA()    |

| Info    | Class constructor. |

| Returns | -                  |

| Errors  | -                  |

| C++:    | ceFPGA::~ceFPGA() |

|---------|-------------------|

| NET:    | _                 |

| Info    | Class destructor. |

| Returns | -                 |

| Errors  | -                 |

| C++:    | HRESULT ceFPGA::LoadBin(const char *pszFileName)                                            |  |  |

|---------|---------------------------------------------------------------------------------------------|--|--|

| NET:    | <pre>Int32 ceFPGA.LoadBin(String sFileName)</pre>                                           |  |  |

| Info    | Load design from pszFileName / sFileName using bin format importer (created via SaveBin()). |  |  |

| Returns | Error Code.                                                                                 |  |  |